vhdl notlari

object types

- signal

- variable

- constant

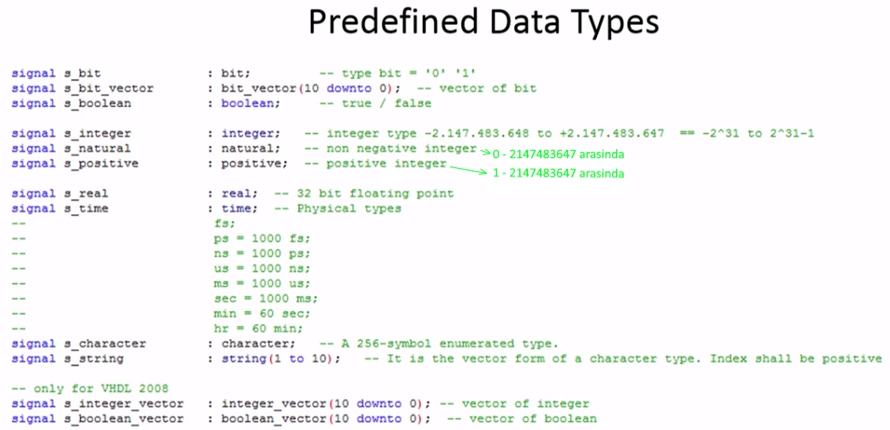

data types

- scalar

- composite

- file

conditional statements

- if

- case

- when

iterative statements

- for loop

- for generate

- while loop

sup program

- function

- procedure

entity

entity blocks can be imagine as boxes with input and output ports.

example:

entity my_entity is

port (

inport_1 : in std_logic;

inport_2 : in std_logic;

outport_1 : out std_logic;

outport_2 : out std_logic

);

end my_entity;

bir entity architecture pair ornegi:

entity and2 is

port (

a : in std_logic;

b : in std_logic;

c : out std_logic

);

end and2;

architecture and2_a of and2 is

begin

c <= a and b after 2ns;

end and2_a;

entity formalize the interface

architecture describe the functionality

bir entity’nin en az bir architecture’i olur; daha fazla da olabilir.

entity – architecture golden rule:

- bir entity’e bir architecture kodun okuma kolayligi acisindan

- entity ile architecture ayni file’da

- entity – architecture çiftine 1 file

- entity ismi ile file ismi ayni isimde mesela and2.vhd

achitecture yapisi:

architecture architecture_name of entity_name is

...

...

begin

...

...

end architecture_name;

architecture içinde signal kullanimi:

Signal wires within a circuit ara teller

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity and_or is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

d : in STD_LOGIC;

e : in STD_LOGIC;

g : out STD_LOGIC);

end and_or;

architecture and_or_a of and_or is

signal c : std_logic;

signal f : std_logic;

begin

c <= a and b;

f <= d and e;

g <= c or f;

end and_or_a;

g = (a and b) or (d and e)

programlama modelleri

- structural :

- hiyerarsik

- block’larin (component) birbirlerine baglanmasi ile buyuk sistemin insasi (component: precompiled entity-architecture pair)

- dataflow :

- output’larin input fonk’lari olarak kullanilmasi.

- boolean equations’larin kullanilmasi

- behavioral :

- algoritmalar ile fonksiyonel programlama

- high level programming gibi.

- Structural

- Dataflow

- Behavioral

1 ve 2 kullanimi internal connections are clear & straight forward smaller designs

3 kullanimi larger designs behaviour of design

- tum design bu 3’unun kombinasyonlari ile yapılır. Behavioral design, structural ve data flow design modellerinin birleşimi ile.

- bunlarin entity’lerinde bir fark yok. Fark sadece architecture’larda.

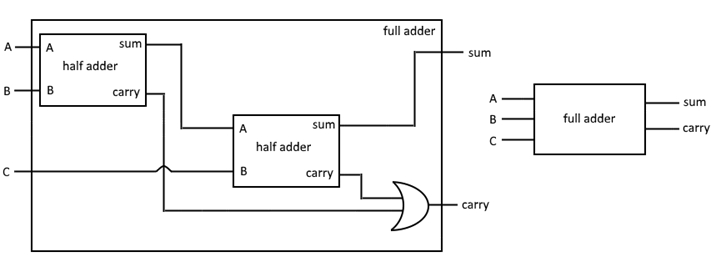

Structural code modelling ornegi: (full adder):

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity half_adder is

port (

a : in std_logic;

b : in std_logic;

sum : out std_logic;

carry : out std_logic

);

end half_adder;

architecture half_adder_a of half_adder is

begin

sum <= a xor b;

carry <= a and b;

end half_adder_a;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity full_adder is

port (

a: in std_logic;

b: in std_logic;

c: in std_logic;

sum: out std_logic;

carry: out std_logic

);

end full_adder;

architecture full_adder_a of full_adder is

component half_adder

port(

a : in std_logic;

b : in std_logic;

sum : out std_logic;

carry : out std_logic

);

end component;

signal sum_1: std_logic;

signal sum_2: std_logic;

signal carry_1: std_logic;

signal carry_2: std_logic;

begin

half_adder_1: half_adder

port map(

a => a,

b => b,

sum => sum_1,

carry => carry_1

);

half_adder_2: half_adder

port map(

a => sum_1,

b => c,

sum => sum_2,

carry => carry_2

);

carry <= carry_1 or carry_2;

sum <= sum_2;

end full_adder_a;

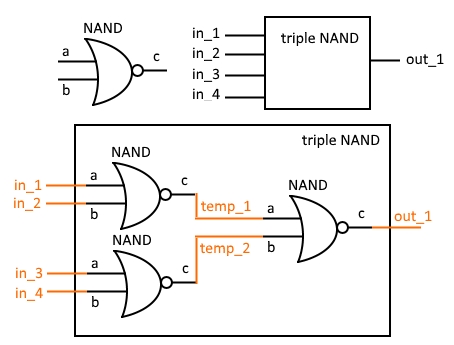

Triple NAND:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity nand_gate is

port (

a : in std_logic;

b : in std_logic;

c : out std_logic

);

end nand_gate;

architecture nand_gate_a of nand_gate is

begin

c <= a nand b;

end nand_gate_a;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity triple_nand_gate is

port (

in_1 : in std_logic;

in_2 : in std_logic;

in_3 : in std_logic;

in_4 : in std_logic;

out_1: out std_logic

);

end triple_nand_gate;

architecture triple_nand_gate_a of triple_nand_gate is

component nand_gate

port(

a : in std_logic;

b : in std_logic;

c : out std_logic

);

end component;

signal temp_1: std_logic;

signal temp_2: std_logic;

begin

nand_1: nand_gate port map (

a => in_1,

b => in_2,

c => temp_1

);

nand_2: nand_gate port map (

a => in_3,

b => in_4,

c => temp_2

);

nand_3: nand_gate port map (

a => temp_1,

b => temp_2,

c => out_1

);

end triple_nand_gate_a;

data flow code modelling ornegi: (half adder)

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity data_flow_modelling is

port( a: in bit;

b: in bit;

sum: out bit;

carry:out bit);

end data_flow_modelling;

architecture data_flow_modelling_a of data_flow_modelling is

begin

sum <= a xor b;

carry <= a and b;

end data_flow_modelling_a;

Behavioral code modelling ornegi: (and gate)

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity behavioral_modelling is

port( a: in std_logic;

b: in std_logic;

c: out std_logic);

end behavioral_modelling;

architecture behavioral_modelling_a of behavioral_modelling is

begin

process (a,b)

begin

if a='1' and b='1' then

c<='1';

else

c<='0';

end if;

end process;

end behavioral_modelling_a;

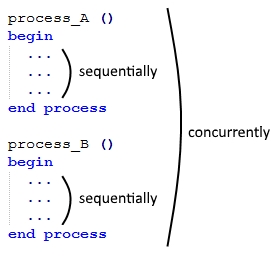

- Behavioral sequentially

- Data flow concurrently

- Structural component hierarchical

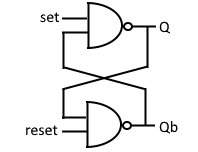

Behavioral model ornegi

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity rs_ff is

port(

set : in bit;

reset : in bit;

q : buffer bit;

qb : buffer bit

);

end rs_ff;

architecture rs_ff_a of rs_ff is

begin

q <= not (qb and set ) after 2 ns;

qb <= not (q and reset) after 3 ns;

end rs_ff_a;

Modelling delay

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity delay_types is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

c : out STD_LOGIC;

d : out STD_LOGIC);

end delay_types;

architecture delay_types_a of delay_types is

begin

c <= a after 2 ns;

d <= transport b after 3 ns;

end delay_types_a;

- intertial delay default delay b <= a after 2 ns;

- eger a değeri 20 ns’den daha hizli değişirse b’de degisme olmaz.

- transport delay b <= transmit a after 2 ns;

- eger a değeri 20 ns’den daha hizli değişirse b de 20 ns sonra a’yi taklit eder.

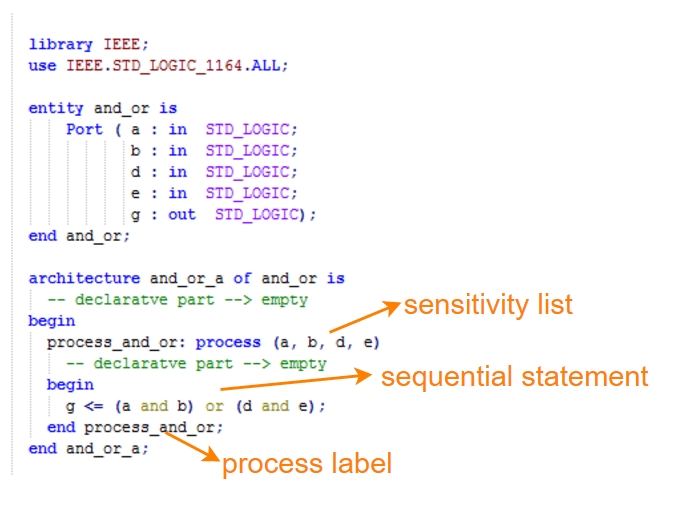

Process kullanimi:

Process is executed in zero time (single simulation cycle)

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity and_or is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

d : in STD_LOGIC;

e : in STD_LOGIC;

g : out STD_LOGIC);

end and_or;

architecture and_or_a of and_or is

-- declaratve part --> empty

begin

process_and_or: process (a, b, d, e)

-- declaratve part --> empty

begin

g <= (a and b) or (d and e);

end process_and_or;

end and_or_a;

- bu kodlama behavioral modelling’dir. Architecture’daki declarative part kisminin bos kalmasindan sunu anlayabiliriz ki kodlar structural değildir. cunku c ve f sinyalleri tanimlanmamis. Behavioral modelling’te bu ek ara sinyallere gerek kalmamis. Yani behavioral model daha high level bir model.

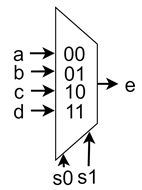

when else ornegi

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity mux_4 is

Port ( a : in bit;

b : in bit;

c : in bit;

d : in bit;

s0 : in bit;

s1 : in bit;

e : out bit;

);

end mux_4;

architecture mux_4_a of mux_4 is

-- declaratve part --> empty

begin

e <= a when (s1 = '0' and s0 = '0') else

b when (s1 = '0' and s0 = '1') else

c when (s1 = '1' and s0 = '0') else

d;

end mux_4_a;

When else with ornegi

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity mux_4_select is

Port ( a : in bit;

b : in STD_LOGIC;

c : in STD_LOGIC;

d : in STD_LOGIC;

s0 : in STD_LOGIC;

s1 : in STD_LOGIC;

e : out STD_LOGIC;

);

end mux_4_select;

architecture mux_4_select_a of mux_4_select is

signal sel : integer;

begin

sel <= 0 when (s1 = '0' and s0 = '0') else

1 when (s1 = '0' and s0 = '1') else

2 when (s1 = '1' and s0 = '0') else

3;

with sel select

e <= a when 0,

b when 1,

c when 2,

d when others;

end mux_4_select_a;

- Generic kodun içinde constant tanimlanmasina benzer.

- Generic’in constant’tan farki constant’lar architecture içinde tanimlanir, architecture içinde kullanılır. generic’ler entity içinde tanimlanir, hem entity içinde hem de architecture içinde kullanılabilir.

Generic’ler entity içinde tanimlanmasi, port tanimlanmalarindan once yapilmalidir

- Kullanim ornegi

entity CPU is

generic (

BusWidth : Integer := 16

);

port(

DataBus : inout Std_Logic_Vector(BusWidth-1 downto 0)

);

......

################

- 2. Kullanim ornegi

entity Gen_Gates is

generic (

Delay : Time := 10 ns

);

port (

In1 : in Std_Logic;

In2 : in Std_Logic;

Output : out Std_Logic

);

end Gen_Gates;

architecture Gates of Gen_Gates is

begin

. . .

Output <= In1 or In2 after Delay;

. . .

end Gates;

- İn sadece okunur sadece giriş

- Out sadece yazılır sadece cikis

- Buffer okunur ve yazılır devrenin içinde sadece 1 sureni olabilir.

- İnput okunur ve yazılır devrenin içinden birden fazla sureni olabilir.

5 design of VHDL

- Assigning x<=y y variable’i x variable’ina veriliyor.

- Reading x<=y x variable’i y variable’inin değerini okuyor.

- driver signal/port bir signal’in bir başka signal’e logic 0 ve logic 1 degerini vermesine deniyor.

- Multiple driver ornegi

- Multiple driver ornegi

ARCHITECTURE ....

SIGNAL A, B, C : bit;

...

A <= B;

A <= C;

...

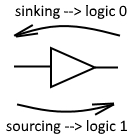

Standart logic types

- U uninitialized initial değer verilmemis

- X unknown logic unknown

- 0 logic 0 sinking current

- 1 logic 1 sourcing current

- Z high impedance no current

- W unknown low logic unknown

- L low logic 0

- H low logic 1

- - dont care

- bit ile std_logic arasindaki fark bit 0 ve 1 degerlerini alirken, std_logic bunlarin haricinde değerler de alabilir. Yani yukarıdaki listedekileri de alabilir.

- Normalde kod icinde kullanilan değerler genelde 0, 1ve Z (high impedance) oluyorlar ama std_logic içindeki diğer değerler de test bench kodlarinda faydali oluyor. Mesela X ve U değerleri.

- logic 0 0 V

- logic 1 5 V, 3 V

- low logic 0 0.3 V, 0.4 V

- low logic 1 4.5 V, 4.2 V, 3.2 V, 2.8 V

#####################

std_logic ile std_ulogic arasindaki fark

- std_logic, std_ulogic’in resolved versionu. Std_ulogic’e unresolved version veya non resolved version deniyor.

- Resolved version multiple assignments to the same object are legal. Asagidaki gibi. (FlagC std_ulogic olsaydı kod calismazdi veya belki de compiler warning verirdi.) yani std_logic std_ulogic’e gore extra ozellige sahip.

Signal FlagC : Std_Logic := 'Z';

ALU : process

begin

. . .

if Carry then FlagC <= '1'; end if;

end process ALU;

Comm : process

begin

. . .

FlagC <= '0';

end process Comm;

- Std_logic ile std_ulogic ayni değerleri alirlar.

- Std_logic vhdl standardi değildir. IEEE 1164 standardi icinde geçer.

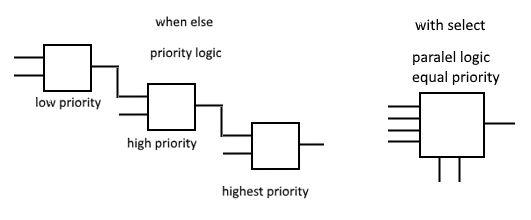

when else ile with select farki

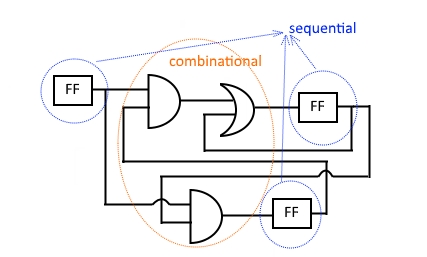

- Process’ler combinational veya sequential olabilirler.

- Combinational and or gate’lerinin kullanilmasi

- Sequential clocked process’lerin kullanilmasi

#####################

Combinational process :

process (a,b,c)

begin

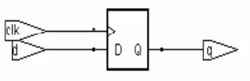

x<=(a and b) or c;

end process;

#####################

Sequential process (clocked process) :

process (clk)

begin

if (clk'event and clk='1') then -– bunun yerine su da kullanilabilirdi if rising_edge(clk) then

Q<=D;

end if;

end process;

- yukarıdaki “if (clk’event and clk=‘1’) then” satiri clk signal’inin rising edge’inde demek.

- ayrica yine yukarıdaki clk bir keyword değildir. Bunun yerine clock_signal de yazılabilirdi.

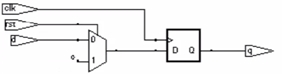

- yukarıdaki clock’lu D flip flop’un vhdl kodu:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity clocked_process is

port(

giris: in std_logic;

yasin_clk: in std_logic;

cikis: out std_logic);

end clocked_process;

architecture clocked_process_a of clocked_process is

begin

process (yasin_clk)

begin

if (yasin_clk' event and yasin_clk='1') then -– bunun yerine su da kullanilabilirdi if rising_edge(yasin_clk) then

cikis<=giris;

end if;

end process;

end clocked_process_a;

#####################

- sequential process’ler içindeki yani clocked process’ler içindeki if’lerde else kullanılmaz. yani asagidaki kullanim yanlis.

process (clk)

begin

if (clk'event and clk='1') then

out1<=a and b;

else

out1<=c;

end if;

end process;

Synchronous reset

- clock’a senkronize olan reset’tir. yani (asagidaki devreye gore) reset high’a alindiginda d flip flop’iu hemen silinmez. Clock’un rising edge’inin gelmesi beklenir.

process (clk)

begin

if (clk'event and clk='1') then

if (rst='1') then

Q <= '0';

else

Q <= D;

end if;

end if;

end process;

#######################

Asynchronous reset

- clock’a senkronize olmayan reset’tir. yani clock’un ne oldgunun onemi olmadan devreye reset atan reset.

process (clk, rst)

begin

if (rst='1') then

Q <= '0';

elsif (clk'event and clk='1') then

Q <= D;

end if;

end if;

end process;

- yani when else mi yoksa if mi kullanilacagi ya da with select mi case kullanilacagi kodlayana bagli. Process kodlanacaksa if ve case’ler kullaniliyor. (soru ??? process içinde hiç when else veya with select gordun mu? Gorduysen buradaki ifade yanlisa duser) Process’lere de combinational ve sequential olabilir deniyor.

- Process içindeki instruction’lar her ne kadar sequential olsa da signal assignment’lari process execution’in sonunda olur.

- Wait process’i sonsuza kadar askıya al demektir.

- Wait on signal signal’de degisme olana kadar askıya al demektir.

- Wait until condition condition sağlanana kadar askıya al demektir.

- Wait for time time kadar sure gecene kadar askıya al demektir.

Only sequential statements can use variables so Variables can only be used inside a process.

- Wait statement ve sensitivity list’ten 2’si birden ayni anda kullanılamaz. Ya biri ya diğeri kullanılır.

- Sensitivity list içinde sadece read edilecek signaller bulunur. Yani buraya out tipinde bir signal yazılamaz. Ve bu signaller static tipinde signaller olmalidir. static signal ???

- sensitiviy list içindeki signallerde degisme olunca process tekrar calisir. Yani repetetive’dir. Yani istersek sensitivity içine signal girilerek, istersek wait statement ile repetetive bir process yazabiliriz.

- hem wait statement hem de sensitivity list process’lere ait bir kavramdır.

process (A,B)

begin

if (A = '1' or B = '1') then

Z <= '1';

else

Z <= '0';

end if;

end process -- suspends at bottom

process

begin

if (A = '1' or B = '1') then

Z <= '1';

else

Z <= '0';

end if;

wait on A,B; -- suspends at wait

end process

2 types of process

- combinational

- clocked

Combinational process ornegi:

process(a,b,c)

begin

x <= (a and b) or c;

end process

clocked process ornegi:

process(clk)

begin

if (clk' event and clk='1') then -- clock signal'inin rising edge'inde

Q <= '0';

end if;

end process

- clocked process’ler içindeki if’lerde else if kullanılmaz.

if statement – when else’in esi

if condition_1 then

--(sequntial statement)

elsif condition_2 then

-- (sequntial statement)

else

-- (sequntial statement)

end if;

process (a,b,c,x)

begin

if (x="0000") then

z<=A;

elsif (x="0101") then

z<=B;

else

z<=C;

end if;

end process;

- 3 level’dan fazla else if kullanmaktan kacin. Time delay cok olmasin diye.

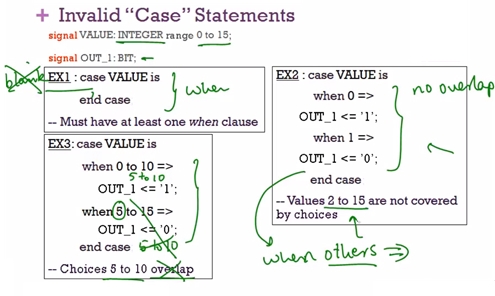

Case statement – with select’in esi

case expression is

when choise_1 => (statement)

when choise_2 => (statement)

when others => (statement)

end case;

process (sel,a,b,c,d)

begin

case sel is

when 0 => y<=a;

when 1 => y<=b;

when 2 => y<=c;

when others => y<=d;

end case;

end process;

#######################

process (a,b,c,x)

begin

case x is

when 0 to 4 => Z<=B; -- range

when 5 => Z<=B;

when 7 | 9 => Z<=A; -- list

when others => Z<=0; -- others

end case;

end process;

#######################

Yanlis case uygulamalari:

#######################

Case içinde null statement: can be used to indicate that when some conditions are met no action is to be performed

case a is

when "00" => q1<='1';

when "01" => q2<='1';

when "11" => q3<='1';

when others <= null; -- no action

end case;

Modelsim’de simulation

- change directory yolu ile calisacak olan directory secimi

- komut vlib work work isminde bir library workspace

- compile için workspace’teki vhd dosyasına cift tiklama

- komut add wave *

- clock force 10 ns

- komut run 50 ns

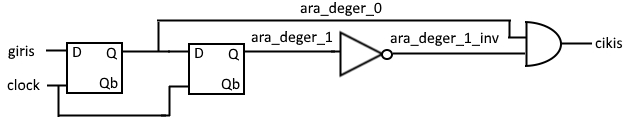

Rising edge detector

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity rising_edge_detector is

port (

clk_input : in std_logic;

giris : in std_logic;

cikis : out std_logic;

);

end rising_edge_detector;

architecture rising_edge_detector_a of rising_edge_detector is

signal ara_deger_0 : std_logic;

signal ara_deger_1 : std_logic;

begin

process_rising_edge_detector : process (clk_input)

begin

if (rising_edge(clk_input)) then

ara_deger_0 <= giris;

ara_deger_1 <= ara_deger_0;

cikis <= (not ara_deger_1) and ara_deger_0;

end if;

end process process_rising_edge_detector;

end rising_edge_detector_a;

Latch flip flop’lari

- aslinda else’leri olmayan if’lerdir. bunlarin kullaniminindan sakınmak gerekli.

process (en, a)

begin

if en='1' then

out1 <= a;

end if;

end process;

#######################

- Yukarıdakinin else’li hali zaten bir mux’tur.

process (en, a)

begin

if en='1' then

out1 <= a;

else

out1 <= '1';

end if;

end process;

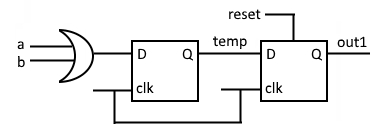

Vhdl kodlarinin hardware modelleri:

- Multiple flip flops: asagidaki kodlarda 2 tane signal assignment var. 2 signal assignment 2 flip flop demektir.

architecture multiple_flip_flops_a of multiple_flip_flops

signal temp : std_logic;

begin

process(clock)

begin

if reset = '1' then

out1 <= '0';

elsif rising_edge(clock) then

temp <= a or b;

out1 <= temp;

end if;

end process;

end multiple_flip_flops_a

#######################

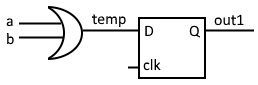

- Using variables as part of clocked process: asagidaki kodlarda 2 signal assignment yok. 1 tane signal assignment var. 1 tane de variable assignment var. Variable assignment demek flip flop demek değildir.

architecture flip_flop_a of flip_flop

begin

process(clock)

variable temp : std_logic;

begin

temp := '0';

if reset = '1' then

out1 <= '0';

elsif rising_edge(clock) then

temp := a or b;

out1 <= temp;

end if;

end process;

end flip_flop_a

- variable’lar process’ler içinde tüketilmelidirler. Yukarıdaki temp variable’i out1 uzerinden tüketiliyor.

- yani yukarıdaki temp variable’i ile a ve b’nin or’lanmis hali temp değişkeni ile bir flip flop üzerinde bekletilmeden direkt aktarilmis oldu.

#######################

Feedback’li devre:

architecture feedback_flip_flop_a of feedback_flip_flop

begin

process(clock)

variable temp : std_logic;

begin

temp := '0';

if reset = '1' then

out1 <= '0';

elsif rising_edge(clock) then

temp := a or out1;

out1 <= temp;

end if;

end process;

end feedback_flip_flop_a

- variable’lar kullanim yerleri sequential logic olarak baglanmis olan flip flop’lar arasinda combinational logic baglantilar varsa bu ara baglantilar variable’lar üzerinden yapılabilir. Bu sayede her bir ara baglanti için flip flop uretilmemis olur.

İslem oncelikleri

- Once not islemleri

- Sonra and islemleri

- En son or islemleri

Yani asagidaki işlemde parantez olsa da olmasa da ayni sonuç cikar.

z = (~ x & y ) | (x & ~y)

z = ~ x & y | x & ~y

Standart Data types

Access type pointer gibi which are created dynamically during simulation and which exact size is not known in advance. Any reference to them is performed via allocators, which work in a similar way as pointers in programming languages

TYPE node; TYPE pointer IS ACCESS node; TYPE node IS RECORD data : INTEGER; link : pointer; END RECORD;

Scalar atomic veri tipleri

- İnteger

- Real

- Enumerated

- Bit

- physics

Composite

- Array

- Record

Types of objects

- Signals

- İnterconnection wires between ports

- Tanimlanma yerleri:

- Packages

- Entities

- Architectures

- Blocks

- Tanimlanma sekli:

- Tanimlanma sekli:

signal signal_name : signal_type;

- değer atanmasi :

- Variables

- Locally store temporary data

- Sadece sequential statement’larda kullanılır.

- Process

- Function

- procedure

- sadece içinde bulunduğu subprogram’dan görülebilir.

- Tanimlanma sekli:

variable variable_name : variable_type;

- değer atanmasi:

- Constants

- Kodun dokumante edilmesini kolaylastirir

- Kodun update edilmesini kolaylastirir.

- Butun declarative vhdl statement’lerinde declare (tanimlanabilir) edilebilir.

- Packages

- Entities

- Architecture

- Process

- Subprogram

- blocks

- tanimlanma sekli:

constant constant_name : constant_type := value;

- Files

- Used to acces file on disk

- Used only in test bench – hardware’da implement edilemez.

- Kullanmak için TextIO package include edilmeli. bu package dosyaya yazma ve okuma islemleri için gerekli olan tum procedure ve function’lari içeriyor.

User defined data types

- user created data type’lari asagidakiler içinde declare edilebilir.

- packages

- entities

- architectures

- processes

- subprograms

- data type’lar 2’ye ayrilir.

- Scalar – tek boyutlu

- Composite – cok boyutlu

-- deger sinirlarini belirleyerek scalar type tanimlamalari

type typ_my_integer is range 0 to 255;

type typ_probability is range 0.0 to 1.0;

type typ_color is (red, yellow, green, black); -- enumerated types

-- signal type'larinin tanimlamalari

signal my_integer: typ_my_integer;

signal probability: typ_probability;

signal color: typ_color;

-- degerlerin atanmasi

my_integer <= 10;

probability <= 0.3;

color <= red;

-----------------------

-- deger sinirlarini belirleyerek vector type tanimlamalari

type typ_vector_real is array (positive range <>) of real;

type typ_integer is array (natural range <>) of integer;

-- degerlerin atanmasi

variable a : typ_vector_real (1 to 3) := (1.0, 2.4, 3.4); -- a has 3 elements

variable b : typ_vector_integer (0 to 1); -- b has 2 elements

-----------------------

-- deger sinirlarini belirleyerek vector type tanimlamasi

type typ_memory is array (0 to 31) of std_logic_vector(15 downto 0);

-- deger sinirlarini belirleyerek matrix type tanimlamasi

type typ_matrix is array (1 to 4, 1 to 5) of integer;

-- hangi degerlerin olacagini belirleyerek sirali liste tanimlamasi

type typ_op is (add, sub, mpy, div, jmp);

-- deger sinirlarini belirleyerek record type tanimlamasi - c'deki structure

type typ_instruction is record;

opcode: typ_op;

src: integer;

dest: integer;

end record;

-- signal type'larinin tanimlamalari

signal memory : typ_memory;

signal matrix : typ_matrix;

signal instruction : typ_instruction;

-- degerlerin atanmasi

memory(0) <= X"1234";

memory(1) <= X"ABCD";

matrix(1,1) <= 5;

instruction.opcode <= add;

instruction.src <= 0;

instruction.src <= 1;

Subtype

- Standart type’larin kullanilmasi ile üretilirler.

- Değer sinirlari limitlemek için kullanılır.

SUBTYPE nibble IS BIT_VECTOR (3 DOWNTO 0);

SUBTYPE byte IS BIT_VECTOR (7 DOWNTO 0);

SUBTYPE word IS BIT_VECTOR (15 DOWNTO 0);

SUBTYPE decimal_digit IS INTEGER (RANGE 0 TO 9);

Array Assignments

Asagidaki (1) ornegi ile (2) ornegi arasinda fark yoktur.

(1) ornegi

SIGNAL z_bus: BIT_VECTOR (3 DOWNTO 0);

SIGNAL a_bus: BIT_VECTOR (1 TO 4);

....

z_bus <= a_bus;

(2) ornegi

z_bus(3) <= a_bus(1);

z_bus(2) <= a_bus(2);

z_bus(1) <= a_bus(3);

z_bus(0) <= a_bus(4);

#######################

SIGNAL z_bus: BIT_VECTOR (3 DOWNTO 0);

SIGNAL a_bus: BIT_VECTOR (1 TO 4);

Legal:

z_bus(3 DOWNTO 2) <= "00";

a_bus(2 TO 4) <= z_bus(3 DOWNTO 1);

Illegal:

z_bus(2 To 3) <= "00"; -- The direction of the slice (i.e. to or downto) must match the direction in which the array is declared.

#######################

SIGNAL z_bus : BIT_VECTOR(3 DOWNTO 0);

SIGNAL a, b, c, d : BIT;

SIGNAL byte : BIT_VECTOR(7 DOWNTO 0);

SIGNAL a_bus : BIT_VECTOR(3 DOWNTO 0);

SIGNAL b_bus : BIT_VECTOR(3 DOWNTO 0);

Legal:

z_bus <= a & b & c & d;

byte <= a_bus & b_bus;

byte <= a_bus & '0' & '0' & '0' & '1';

Illegal:

byte <= a_bus & c;

#######################

SIGNAL z_bus : BIT_VECTOR(3 DOWNTO 0);

SIGNAL a, b, c, d : BIT;

SIGNAL byte : BIT_VECTOR(7 DOWNTO 0);

Asagidaki (1) ornegi ile (2) ornegi arasinda fark yoktur.

(1) ornegi

z_bus <= (a, b, c, d);

(2) ornegi

z_bus(3) <= a;

z_bus(2) <= b;

z_bus(1) <= c;

z_bus(0) <= d;

Signed - unsigned

Bir unsigned sayinin signed halini bulma

011 = 3 bunun tumleyenini al 100 bunu 1 ile topla 100 + 001 = 101 101 = -3

Type conversion – casting

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

signal w_signed : signed(7 downto 0);

signal w_unsigned : unsigned(7 downto 0);

signal w_integer : integer;

signal w_stlv : std_logic_vector(7 downto 0);

w_signed <= to_signed(w_integer, 8); -- convert integer to signed

w_unsigned <= to_unsigned(w_integer, 8); -- convert integer to unsigned

w_unsigned <= unsigned(w_signed); -- type casting signed to unsigned

w_stlv <= std_logic_vector(w_signed); -- type casting signed to std_logic_vector

w_integer <= to_integer(unsigned(w_stlv)); -- convert std_logic_vector to integer, with unsigned casting

İterations

- For loop known number of iterations

- While loop unknown number of iterations

- For loop usage

my_label: for index in a_range loop

-- sequential statements ...

end my_label;

- while loop usage

my_label: while index (condition) loop

-- sequential statements ...

end my_label;

#######################

for example (1) – 0’dan 10’a kadarlik bir loop içinde atomic değişkene atama

variable acc: integer;

...

...

acc := 0;

filter_loop : for i in 0 to 10 loop

acc := acc + x(i)*h(i);

end loop filter_loop;

for example (2) – başka bir vector’un uzunluğuna gore degisen bir loop içinde atomic bir değişkene atama

signal x : std_logic_vector(7 downto 0);

...

...

variable par : std_logic;

par := '0';

parity_loop : for i in 0 to x'length-1 loop

par := par xor x(i);

end loop parity_loop;

for example(3)- 0’dan 10’a kadarlik bir loop içinde vectorel değişkene atama

type typ_square is array (0 to 10) of integer;

signal square : typ_square;

...

...

square_loop : for i in 0 to 10 loop

square(i) <= i*i;

end loop square_loop;

- yukarıdaki (1) ve (2) orneklerinde acc ve par variable’lari signal olarak kullanılamazlar cunku ust uste atama mevcut. Galiba signallerde bu yapilamiyor. (???)

- (3) orneginde ise square signal’i istenirse variable olarak kullanılabiliyor.

#######################

While example (1) – file sonuna kadar loop

read_loop : while (not_end_of_file) loop

...

-- read from file

...

end loop read_loop;

While example (2) – iterasyon sayisi belli olduğunda kullanim

type typ_square is array (0 to 10) of integer;

signal square : typ_square;

...

...

variable i : integer;

square_loop : while (i <= 10) loop

square(i) <= i*i;

i := i+1;

end loop square_loop;

#######################

exit ve next statements

example (1)

type typ_square is array (0 to 10) of integer;

signal square : typ_square;

...

...

square_loop : for i in 0 to 15 loop

exit when (i=11);

square(i) <= i*i;

end loop square_loop;

example (2)

type typ_square is array (0 to 10) of integer;

signal square : typ_square;

...

...

square_loop : for i in 0 to 15 loop

if (i=11) then

exit square_loop; -- buradaki loop label'i optional.

end if;

square(i) <= i*i;

end loop square_loop;

- (1) ve (2) example’lari arasinda fark yok. Biri exit –when ile yapılırken diğeri if-exit ile yapilmis.

Example (2)

square_loop : for i in 0 to 15 loop

next square_loop when (i=5); -- index 5 iken calismaz sonraki satira atlar.

exit square_loop when (i=10);

square(i) <= i*i;

end loop square_loop;

Assert statement

- Aciklama tasarimciya consol’dan rapor vermeye yarar.

kullanimi:

assertion_statement ::= assert condition

[report expression]

[severity expression]

- Assert condition kismindaki condition sonucu false olduğunda rapor sistemi calisir.

- Report expression kismindaki report clause kismi bos ise “assertion violation” yazar

- Severity expression kismindaki severity clause kismi bos ise “error” yazar

- Note model calisma durumunun mevcut halinin bilgisinin verilmesinde mesela dongunun yüzde ne kadar calistiginin bilgisi

- Warning cok tehlikeli olmayan condition’larin bilgisinin verilmesinde. Modellemenin yanlis bir davranisa doğru gittiği durumlarda mesela beklenen değerden farkli bir değer veren sinyalin olduğu durumlarda.

- Error modelin calismayacagi veya yanlis calisacagi condition’larin bilgisinin verilmesinde mesela bir operation’in pozitif yerine negatif değer vermesi.

- Failure model icin tehlikeli etkilerin olusacagi durumlarin bilgisinin verilmesinde mesela sifira bolme durumunda mesela array içinde gösterilen adresin array boyutundan daha buyuk olmasi durumunda

- Fatal vhdl standartlarinda olmayan kodlarda simulator tarafında define edilen durumlarda run time error condition’larinda

#######################

Ornek 1:

signal x1: std_logic;

signal x2: std_logic;

signal y: std_logic;

assert y = (x1 xor x2) -- assertion if y different from (x1 xor x2)

report "y check error"

severity Error;

ciktisi:

** Error: Y check error

Time: 40 ns Iteration: 0 Instance:/ tb1

#######################

Ornek 2:

-- asagidaki ornekte yukaridakinden farkli olarak, simulator x1 ve x2 signal'lerinin degerlerini string olarak bildiriyor.

assert y = (x1 xor x2)

report "y check error: error at: x1=" & std_logic'image(x1)&

x2=" & std_logic'image(x2)

severity Error;

ciktisi:

** Error: Y check: error at: x1='1' x2='1'

Time: 40 ns Iteration: 0 Instance:/ tb1

subprogram procedure ve function

- Hem function hem procedure sequential’dir.

- Return etmeleri

- function

- as the value of function

- function

- procedure

- global objects

- by storing values into formal parameters

- functions do not change their formal parameters

#######################

Procedure syntax

Procedure declaration

procedure procedure_example (

constant A : in integer;

signal B : inout bit_vector;

variable C : out real;

D : file );

- in direction’i icin default type constant

- out direction’i icin default type variable

- yani type yazilmadigi zaman degerlere kendiliğinden bu type’lar atanir.

Procedure definition

procedure identifier [(formal parameter list)] is

-- [declarations]

begin

-- sequential statements

end procedure identifier;

Procedure body

- procedure declaration’lari icinde signal kullanilmaz cunku signal’ler sadece concurrent kisimlarda calisir. Procedure ise concurrent degil sequential’dir ama formal parameter list icinde kullanilabilir.

#######################

Function syntax

- asagidaki gibi de declare edilebilir.

function rand return float;

- asagidaki gibi de declare edilebilir.

function sum (

A: integer;

B: integer) return integer;

- function’lar sadece 1 argument return edebilir. Procedure’ler boyle degildir. Procedure’ler formal parameter list’teki veriler uzerinden ve global veriler uzerinden deger return edebilirler.

- Function’larda kullanilan formal parameters sadece in modunda kullanilabilir.

- Bir function en az 1 tane return parameter bulundurmalidir.

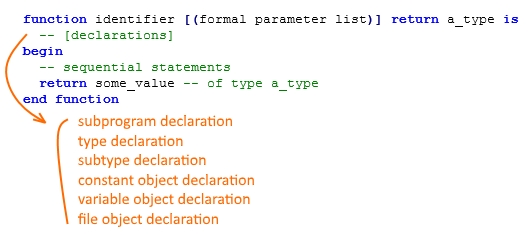

Function body

function identifier [(formal parameter list)] return a_type is

-- [declarations]

begin

-- sequential statements

return some_value -- of type a_type

end function

- Function declaration’lari icinde (ayni procedure’lerde oldugu gibi) signal kullanilmaz cunku signal’ler sadece concurrent kisimlarda calisir. Procedure ise concurrent degil sequential’dir ama formal parameter list icinde kullanilabilir.

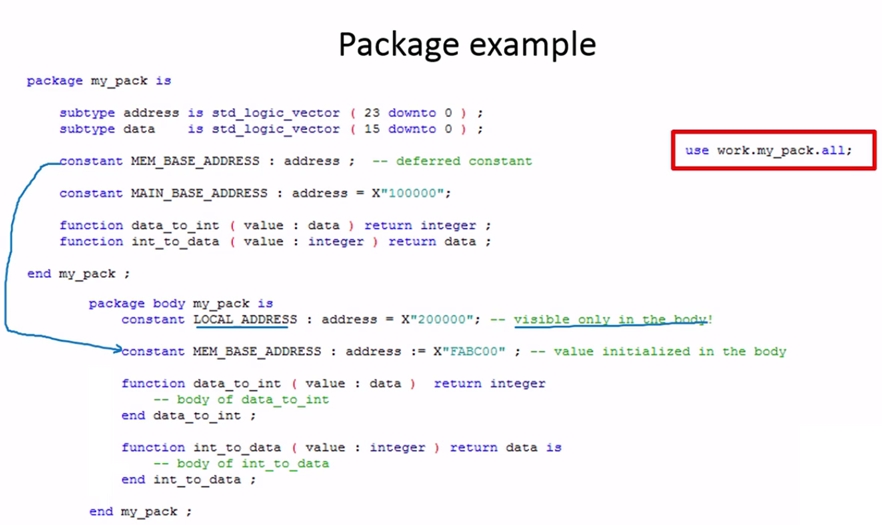

Packages

- Bu element paketleri 2 veya daha fazla design unit’te paylasilabilir. Package bu ise yarar.

- Package icindeki (mesela subprogram) detaylari user’dan saklanabilir. User sadece package icindeki interface’i gorur.

- Package declaration interface tanimlar

- Package body behaviour tanimlar

#######################

Package syntax

Package declaration

package package_name is

-- declaration of

-- types and subtypes

-- subprograms

-- constants

-- signals

-- etc.

end package_name;

package body - definition

package body package is

-- definition of previously declared

-- constants

-- subprograms

-- declaration/definition of additional

-- types and subtypes

-- subprograms

-- constants

-- signals

-- etc.

end package_name;

- User’in gormesini istemedigi constant degerlerin atamalari ve subprogramlarin definition’lari package body’de

- Ayni sekilde eger hic bir bilgiyi package declaration’da vermek istenmiyorsa hepsi (veya ek olarak) package body’de verilebilir.

- Package body icinde tanimlanan element’ler package disinda kullanilamazlar. Mesela ornekteki LOCAL_ADDRESS constant’i

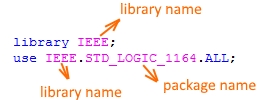

- Package’in koda import edilmesi

use work.my_pack.all;

#######################

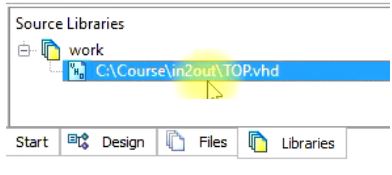

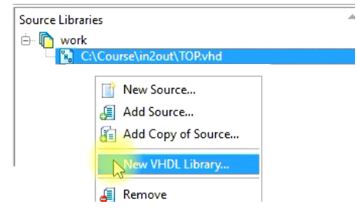

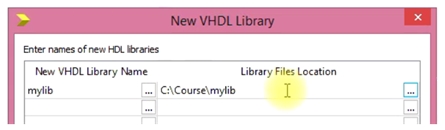

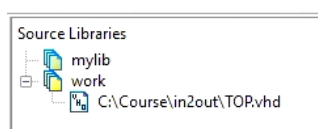

- Kendi library’ni olusturmak icin:

- Mypackage’i mylib icine surukle

Generate Statement

- concurrent statement’tir.

- Circuit part olarak dusunulebilir.

- Concurrent statement’larin icine gomulur.

- Bilhassa parametreli tasarimlarda kullanilir.

- 2 farkli generate statemen var

- For statement

- İf statement

- bunlar aslinda fpga’da buyuk projelerin nasil yazildiginin adam gibi anlasildigi kisim. yani adamlar bu generate statement’larini kullanarak kucuk register parcalarindan cok buyuk projeler tasarlayabiliyorlar.

for generate statement syntax:

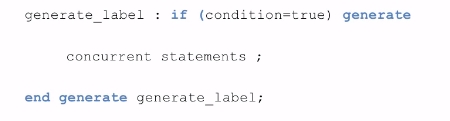

if generate statement syntax:

#######################

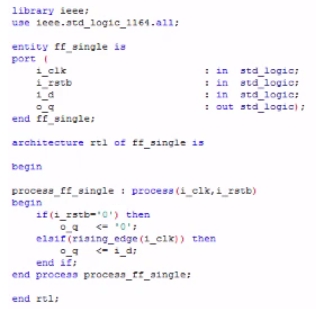

For generate statement ornegi :

tekli flip flop tarafi:

tekli flip flop tarafindan for generate statement ile N kadar uretilen kisim:

#######################

if generate statement ornegi :

tekli flip flop tarafi:

tekli flip flop tarafindan if generate statement ile uretilen kisim: